Complex Digital Systems

As taught in: Spring 2005

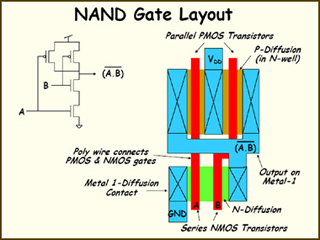

NAND gate layout from Lecture 3: CMOS Technology and Logic Gates. (Image by Professors Arvind and Asanovic.)

Instructors:

Prof. Chris Terman

(Contributor)

Prof. Krste Asanovic

Prof. Arvind

MIT Course Number:

6.884

Level:

Course Features

Course Highlights

This course features a complete set of lecture notes. In addition, labs are also available.

Course Description

This course is offered to graduates and is a project-oriented course to teach new methodologies for designing multi-million-gate CMOS VLSI chips using high-level synthesis tools in conjunction with standard commercial EDA tools. The emphasis is on modular and robust designs, reusable modules, correctness by construction, architectural exploration, and meeting the area, timing, and power constraints within standard cell and FPGA frameworks.